Apple has officially introduced the Apple Silicon M5 Pro and M5 Max, and these chips represent more than just the next iteration of the Pro and Max lineup. They introduce several major architectural changes, including a new Fusion architecture, a redesigned CPU microarchitecture, and a different approach to scaling Apple Silicon.

Let’s break down what makes the M5 Pro and M5 Max so different.

A New Fusion Architecture

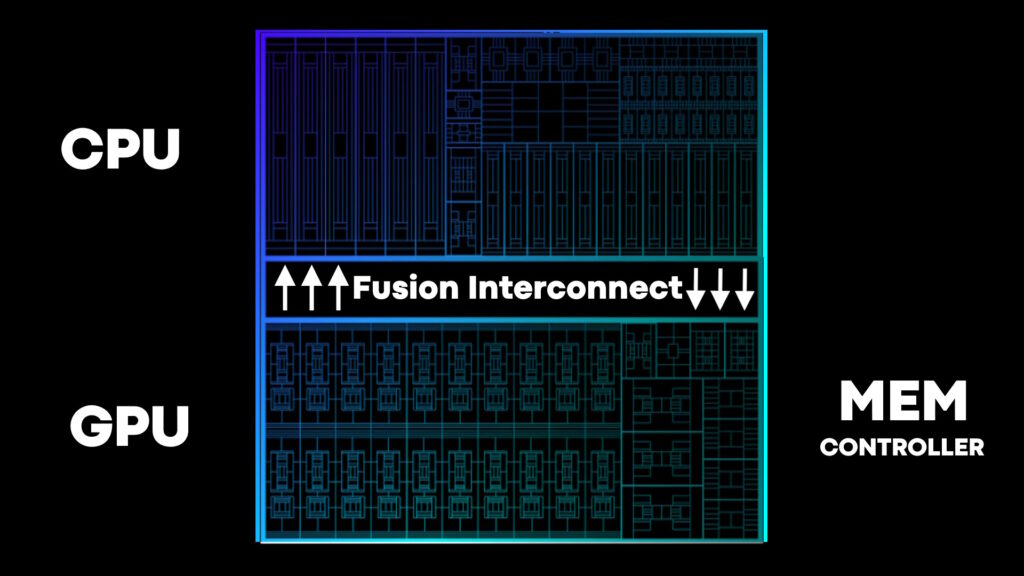

One of the most significant changes in the M5 Pro and M5 Max is the introduction of Apple’s new Fusion architecture.

Apple has used the term Fusion before. In earlier generations, Fusion was mainly used to scale chips, for example, combining two Max chips to create an Ultra chip.

With the M5 generation, Apple is using Fusion in a different way.

Instead of simply scaling up existing chips, the new architecture:

- Combines two separate dies into a single SoC

- Uses third-generation 3-nanometer process technology

- Connects the dies with high-bandwidth, low-latency advanced packaging

Once combined, the chip functions as a single system-on-chip that integrates:

- CPU

- GPU

- Media engine

- Unified memory controller

- Neural engine

- Thunderbolt 5 controller

This design is conceptually similar to the chiplet approach used by Intel and AMD, where different parts of the processor are manufactured separately and then packaged together.

The advantage is that Apple can design and manufacture CPU and GPU dies independently, improving manufacturing yields and flexibility.

The M5 Pro: CPU Architecture Changes

The M5 Pro introduces a new CPU structure built on Apple’s third-generation 3 nm process.

The chip features:

- 6 Super Cores

- 12 Performance Cores

- 20-core GPU

But the naming change is important.

Super Cores Replace Performance Cores

Previously Apple used:

- Performance cores

- Efficiency cores

In the M5 Pro, Apple has shifted the hierarchy upward:

| Previous Naming | New Naming |

|---|---|

| Performance cores | Super cores |

| Efficiency cores | Performance cores |

However, the new performance cores are not simply renamed efficiency cores.

Instead:

- They are derived from the new super-core architecture

- They share more of the same design DNA

- They are significantly more powerful than previous efficiency cores

This effectively creates a “big-core-only” architecture, similar to approaches used by companies like MediaTek in some designs.

A Chiplet-Style Layout

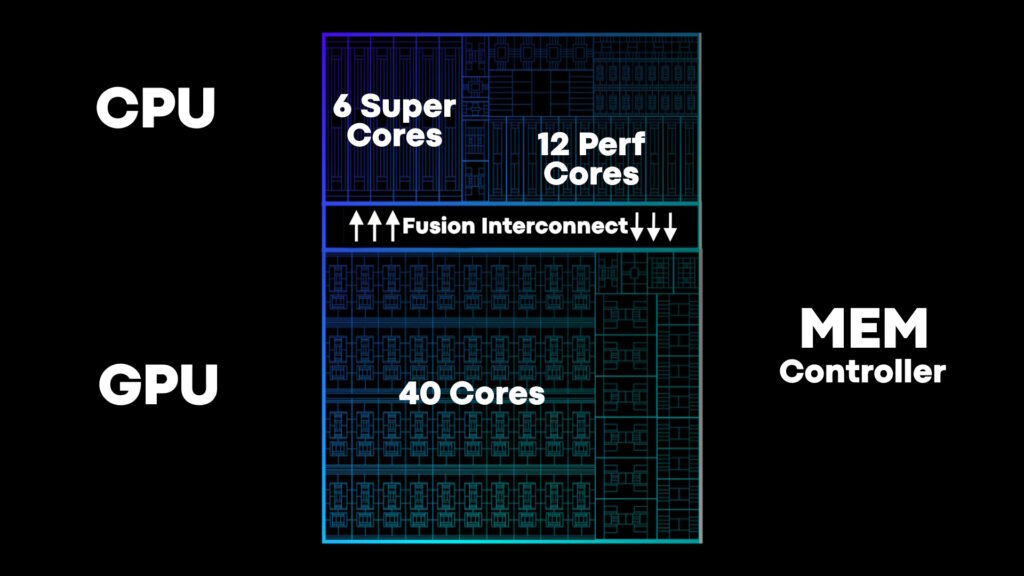

The M5 Pro appears to be constructed from two main dies:

CPU Die

- 6 Super cores

- 12 Performance cores

GPU / System Die

- 20-core GPU

- memory controller

- media engines

- system interfaces

These two dies are then connected using the Fusion interconnect, forming a single SoC package.

This modular design lets Apple optimize the CPU and GPU components independently before combining them.

The M5 Max

The M5 Max keeps the same CPU configuration as the M5 Pro but significantly increases GPU power.

M5 Max specifications

- Third-generation 3 nm process

- 6 Super cores

- 12 Performance cores

- Up to 40-core GPU

In other words, the CPU architecture is identical to the M5 Pro. The main difference is the larger GPU subsystem.

How the CPU Layout Has Changed

Compared with the previous generation, the CPU core structure is noticeably different.

M4 Generation

| Chip | CPU Configuration |

|---|---|

| M4 Pro | 10 Performance + 4 Efficiency |

| M4 Max | 12 Performance + 4 Efficiency |

M5 Generation

| Chip | CPU Configuration |

|---|---|

| M5 Pro | 6 Super + 12 Performance |

| M5 Max | 6 Super + 12 Performance |

Instead of mixing large and small cores, Apple now focuses on two levels of high-performance cores, both derived from the same architecture.

Performance Improvements

CPU Performance

Apple reports:

- M5 Pro:

- 30% higher multi-threaded performance than M4 Pro

- M5 Max:

- 15% higher multi-threaded performance than M4 Max

The smaller gain for the Max version makes sense because both chips now share the same CPU configuration.

Single-core performance matches the standard M5, since the same core design is used.

GPU Performance

The GPU improvements are much more significant.

Apple claims:

- Up to 4× peak GPU compute for AI workloads compared to M4 Pro / M4 Max

- 6× peak GPU compute vs M1 Max

For graphics workloads:

- M5 Pro GPU

- 20% faster than M4 Pro

- 2.2× faster than M1 Pro

- M5 Max GPU

- 20% faster than M4 Max

- 2.2× faster than M1 Max

The chips also feature third-generation hardware ray tracing, providing about 30% higher ray-tracing performance than the M4 series.

Memory Capacity and Bandwidth

Memory capacity has also increased.

| Chip | Maximum Memory |

|---|---|

| M5 | 32 GB |

| M5 Pro | 64 GB |

| M5 Max | 128 GB |

Memory bandwidth scales with capacity thanks to Apple’s unified memory architecture.

Maximum Memory Bandwidth

| Chip | Bandwidth |

|---|---|

| M5 | up to 153 GB/s |

| M5 Pro | up to 307 GB/s |

| M5 Max | up to 614 GB/s |

Apple achieves this by adding additional memory controllers as memory capacity increases.

For workloads that access large datasets, such as large language models or complex rendering tasks, this architecture allows extremely high throughput.

Available Devices

Currently, the M5 Pro and M5 Max are available in:

- 14-inch MacBook Pro

- 16-inch MacBook Pro

Both models offer multiple configurations with different numbers of CPU and GPU cores depending on the selected option.

Final Thoughts

The M5 Pro and M5 Max represent one of the most significant architectural changes Apple has made to its silicon lineup.

Key highlights include:

- A new Fusion chiplet architecture

- Redesigned CPU core hierarchy

- 6 Super cores + 12 Performance cores

- Up to a 40-core GPU

- Up to 128 GB unified memory

- Up to 614 GB/s memory bandwidth

Perhaps the biggest shift is that the Pro and Max chips are no longer just scaled-up versions of the base M-series chip. Instead, they now use distinct architectures designed specifically for higher-end systems.

This approach could shape how Apple builds future chips, especially if it expands the Fusion architecture further for future Ultra or workstation-class processors.

Gladstone is a tech virtuoso, boasting a dynamic 25-year journey through the digital landscape. A maestro of code, he has engineered cutting-edge software, orchestrated high-performing teams, and masterminded robust system architectures. His experience covers large-scale systems, as well as the intricacies of embedded systems and microcontrollers. A proud alumnus of a prestigious British institution, he wields a computer-science-related honours degree.